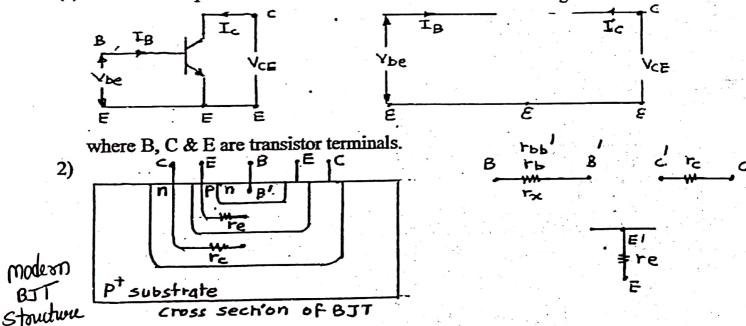

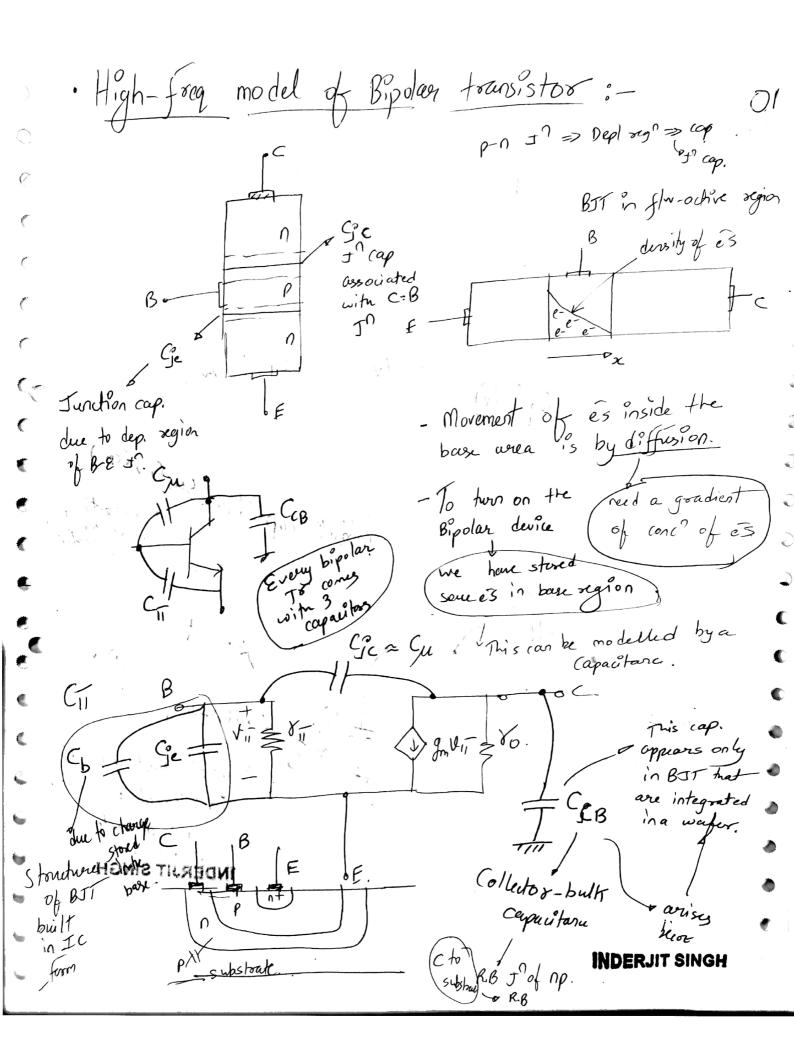

**HF Model of BJT**: Model is a two port network (TPN) consists of RLC voltage source & current source. Each and every component in BJT model represents physical phenomenon or characteristics of transistor.

Step by step formation of model:

(1) Let us develop HF model of transistor connected in CE configuration

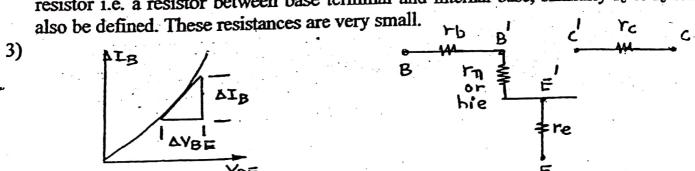

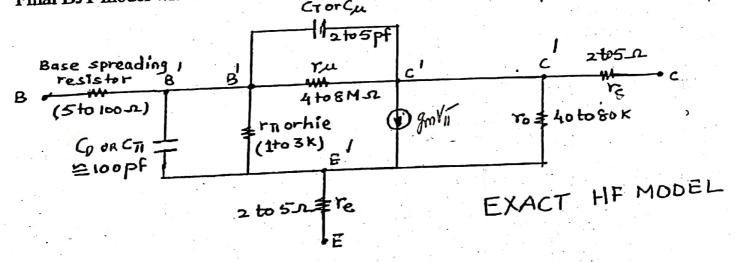

B', C', E' are idealized internal base collector and emitter,  $r_b \to$  base spreading resistor i.e. a resistor between base terminal and internal base, similarly  $r_c \& r_c$  can also be defined. These resistances are very small.

Input characteristic of BJT indicates that as  $V_{BE}$  increase,  $I_{B}$  increases exponentially. Inverse of slope of characteristic at Q point represent input resistance of BJT. This point is represented in BJT by connecting a resistance between B' & E'. This is known as input resistance of BJT.

$$h_{ie} = r_{\pi} = \frac{1}{slope} = \frac{\Delta V_{BE}}{\Delta I_B} \bigg|_{\Delta V_{CE} = 0}$$

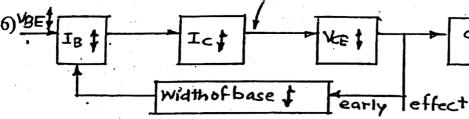

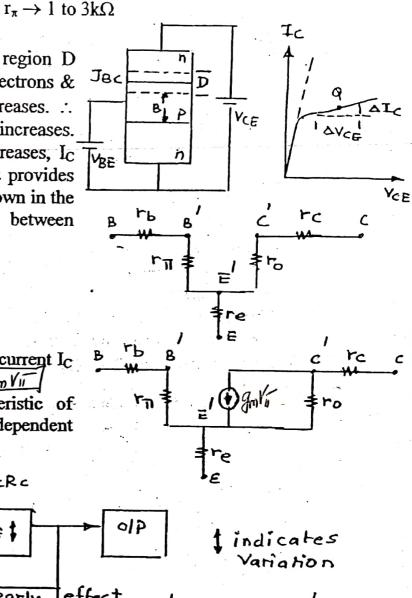

4) As  $V_{CE}$  increases, width of depletion region D increases, width of base B decreases, electrons & hole recombination in base region decreases. In number of electron drifting to collector increases. This increases  $I_C$ . It means as  $V_{CE}$  increases,  $I_C$  increases. This is due to early effect & provides slope of charac. This phenomenon is shown in the

model by connecting a resistance  $r_0$  between C' & E' where.

$$r_o = \frac{1}{slope} \bigg|_{Qpt} = \frac{\Delta V_{CE}}{\Delta I_C} \bigg|_{\Delta IB=0}$$

$r_o \rightarrow 40$  to  $80k\Omega$

5) BJT is a current control device. Output current  $I_C$  is controlled by input current  $I_B$ .  $\boxed{\int c = g_m V_{\parallel}}$  i.e.  $I_C = h_{fe}I_B = \beta I_B$ . This characteristic of transistor is shown in model by a dependent current source.

$\beta$  or  $h_{fe} \rightarrow 20$  to 300.  $V_{CE=V_{CC}-I_{CR}}$

As  $V_{BE}$  varies,  $I_B$  varies since  $I_C = \beta I_B$ ,  $I_C$  varies this changes  $V_{CE}$ . Variation in  $V_{CE}$  changes reverse bias potential across  $J_{BC}$ . This causes variation in base width, which finally changes  $I_B$ . It means change in output i.e.  $V_{CE}$  causes change in input  $(I_B)$ . This indicates feedback between output to input. This internal feedback of BJT is represented in model by connecting a resistance  $r_{\mu}$  between input & output [C' & B']  $r_{\mu} \to 4$  to  $8M\Omega$

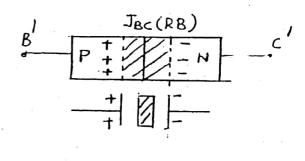

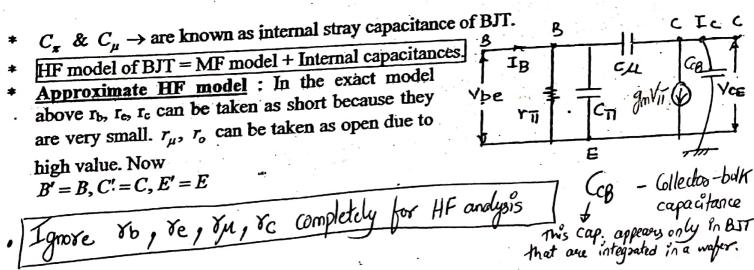

- 7) Junction J<sub>BE</sub> is reverse bias. This causes an appreciable depletion region to exists across junction. Depletion region doesn't have any free electron in it. ∴ this behaves like insulator and works as dielectric, while P region and N region works as plate with +ve and -ve charges. This forms a capacitance between C' & B'. This is known as transition capacitance (C<sub>T</sub> or C<sub>µ</sub>).

- 8) At LF time per cycle is more.

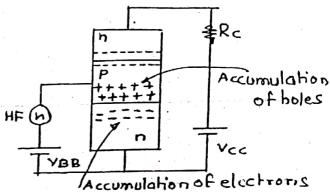

Therefore time available for electron to diffuse through J<sub>BE</sub>, move through base region and drift to collector is large. But at high frequency time per cycle is less.

electron coming from E did not get enough time to diffuse through J<sub>BE</sub>. Similarly holes coming from collector did not get enough time to diffuse through forward biased J<sub>BE</sub>. This causes accumulation of electrons on E side of J<sub>BE</sub>, while holes gets accumulated on B side of J<sub>BE</sub>. This phenomenon of charge storage around forward biased J<sub>BE</sub> is represented in model by a capacitor between B' & E' known as diffusion capacitance C<sub>x</sub> or C<sub>D</sub>.

Final BJT model with transition & diffusion capacitance is shown below.

Bipolar Transistor (aps Internal Contacts (Cus Cir, Cip)

(HF modu)

B

Vin Stir (Aps Internal Contacts of the contact of the

Wires at IP & of wire at high

of amplifius are

at different ys & There

exists a capacitance wire at low

potential

between wires

Course

Of wiring capacitance

Course

Of wiring capacitance

(wo — of wiring capacitances)

Course

Therefore, there

exists a capacitances

Course

Of wiring capacitances

Course

Of wiring capacitances

Course

Of wiring capacitances

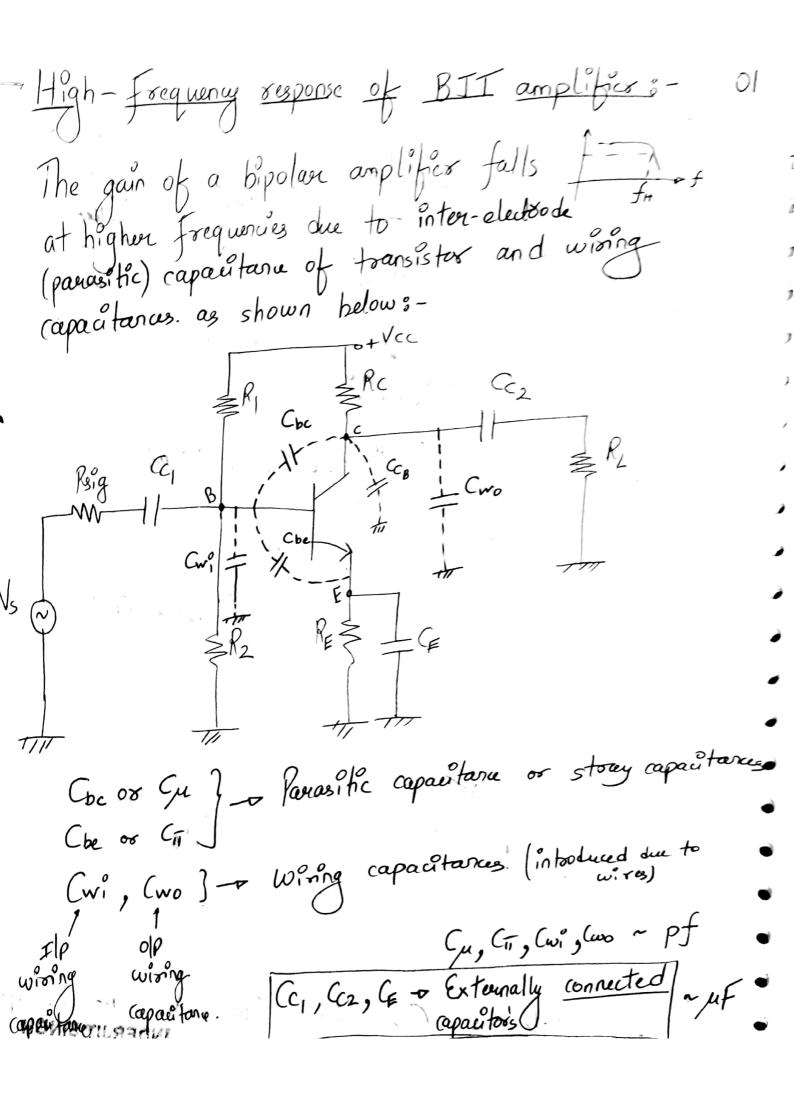

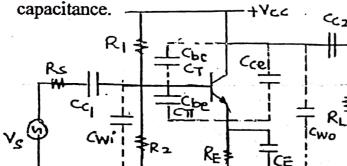

Circuit diagram of amplifier with all stray

$C_{C1}$ ,  $C_{C2}$ ,  $C_E \rightarrow$  connected capacitors  $C_T$ ,  $C_{\pi}$ ,  $C_{ce}$ ,  $C_{wi}$ ,  $C_{wo} \rightarrow stray$ , parasitic, fictitious capacitor.

$\rightarrow$  in  $\mu$ f. connected caps  $\rightarrow$  in pf. stray caps

## STATUS OF CAPACITORS IN DIFFERENT FREQUENCY RANGE

- $DC \rightarrow (f=0) \rightarrow X_C = \frac{1}{2\pi fC} = \infty \rightarrow \text{all connected and stray caps are open.}$

- $(LF) \rightarrow \text{very low frequency (few hertz)} \rightarrow X_C = \frac{1}{2\pi (Hertz)(\mu f)}$  neither very low

nor very high : connected capacitor are considered

$$\rightarrow X_C = \frac{1}{2\pi (Hertz)(pf)} = \text{very high}$$

: at LF stray capacitors are open.

$MF \rightarrow Mid$  frequency (few 100's of KHz)

$$\rightarrow X_C = \frac{1}{2\pi \left(100 \times 10^3 \, Hz\right) \left(\mu f\right)} = \text{very low}$$

- connected capacitors are short,  $X_C = \frac{1}{2\pi (100 \times 10^3)(pf)} = \text{high}$

- stray capacitors are open.

- HF  $\rightarrow$  high frequency (100's of MHz)  $\rightarrow X_C = \frac{1}{2\pi (MHz)(\mu f)}$

- connected capacitors are shorted,  $X_C = \frac{1}{2\pi (MHz)(pf)} = \text{high}$

- stray caps are neither short nor open but considered.