| Experiment | 3                                         |

|------------|-------------------------------------------|

| Number     |                                           |

| Aim        | Draw and simulate layout for 6T SRAM cell |

| Apparatus  | PC loaded with Microwind Tool             |

| Required   |                                           |

| 11/1       |                                           |

Circuit Diagram and Stick diagram on the blank side

## Theory:

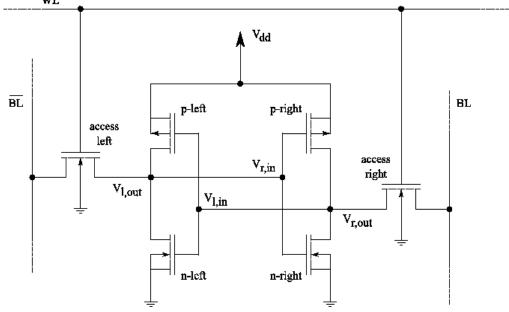

Static random access memory (SRAM) can retain its stored information as long as power is supplied. This is in contrast to dynamic RAM (DRAM) where periodic refreshes are necessary or non-volatile memory where no power needs to be supplied for data retention, as for example flash memory. The term ``random access'' means that in an array of SRAM cells each cell can be read or written in any order, no matter which cell was last accessed. The structure of a 6 transistor SRAM cell, storing one bit of information, can be seen in the given Figure. The core of the cell is formed by two CMOS inverters, where the output potential of each inverter Vout is fed as input into the other Vin. This feedback loop stabilizes the inverters to their respective state.

The access transistors and the word and bit lines, WL and BL, are used to read and write from or to the cell. In standby mode the word line is low, turning the access transistors off. In this state the inverters are in complementary state. When the p-channel MOSFET of the left inverter is turned on, the potential V1, out is high and the p-channel MOSFET of inverter two is turned off, Vr, out is low.

To write information the data is imposed on the bit line and the inverse data on the inverse bit line,  $\overline{BL}$ . Then the access transistors are turned on by setting the word line to high. As the driver of the bit lines is much stronger it can assert the inverter transistors. As soon as the information is stored in the inverters, the access transistors can be turned off and the information in the inverter is preserved.

For reading the word line is turned on to activate the access transistors while the information is sensed at the bit lines.

| Sensea at the sit mes. |                                                                                                 |

|------------------------|-------------------------------------------------------------------------------------------------|

| Procedure              | 1. Draw the circuit diagram and stick diagram of 6T SRAM                                        |

|                        | <ol><li>Draw the layout according to lambda based design rules in<br/>microwind tool.</li></ol> |

|                        | <ol><li>Activate WL by connecting it to Vdd.</li></ol>                                          |

|                        | 4. Apply clock input on BL and inverted clock input on $\overline{\mathrm{BL}}$ .               |

|                        | 5. Observe the output on both output nodes.                                                     |

| Conclusion:            |                                                                                                 |

|                        |                                                                                                 |