# Trends in Integrated Circuits Technology

#### IC DEVICE TECHNOLOGY OVERVIEW

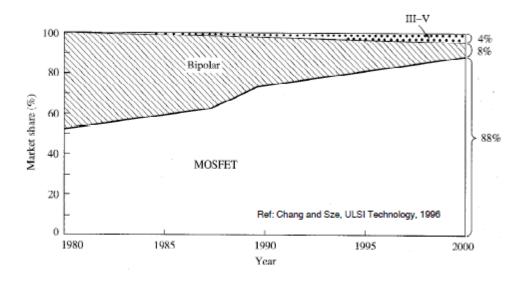

There are a variety of major manufacturing process technologies (Figure 4-1) used in design and fabrication of silicon-based integrated circuits (ICs). These include metal-oxide-semiconductor (MOS), bipolar, and combined bipolar and complementary-MOS (BiCMOS). While silicon-based processing dominates in semiconductor manufacturing, gallium arsenide (GaAs), a compound-semiconductor material, is a niche alternative to silicon for some applications.

| IC<br>Manufacturing     |                                                                                    | Marketshare<br>(Percent of Total Dollars) |      |      |               |                |  |

|-------------------------|------------------------------------------------------------------------------------|-------------------------------------------|------|------|---------------|----------------|--|

| Process<br>Technologies | 1997 Status                                                                        |                                           | 1980 | 1990 | 1997<br>(EST) | 2002<br>(FCST) |  |

| MOS (total):            |                                                                                    |                                           | 52   | 75   | ~69           | ~87            |  |

| PMOS                    | Obsolete                                                                           | 31                                        | 5    | -    | _             | _              |  |

| NMOS/HMOS               | Virtually obsolete                                                                 | 2                                         | 37   | 10   | ব             | <1             |  |

| CMOS                    | Mainstream MOS technology, with continued growth.                                  | 2                                         | 10   | 65   | 69            | 86             |  |

| Bipolar (total):        |                                                                                    | 65                                        | 48   | 24   | ~12           | ~10            |  |

| ECL                     | Fastest silicon-based process, but losing to GaAs. Virtually obsolete.             | 3                                         | ø    | 3    | ব             | ব              |  |

| TTL                     | Virtually obsolete.                                                                | 29                                        | 8    | 2    | <1            |                |  |

| S/LS TTL                | Virtually obsolete, having lost to MOS ASICs designs.                              | 7                                         | 13   | 4    | 1             | ব              |  |

| LINEAR                  | Mainstream analog technology, but competition from CMOS, and GaAs.                 | 26                                        | 24   | 15   | 11            | 8              |  |

| BiCMOS:                 | Offers both MOS and bipolar advantages, but<br>slipping from high cost/complexity. |                                           | -    | 1    | 18            | 5              |  |

| GaAs:                   | Still niche technology, but future potential.                                      | _                                         | -    | ব    | 1             | 1              |  |

Source: ICE 11218W

Figure 4-1. Market Share Overview of IC Manufacturing Process Technologies

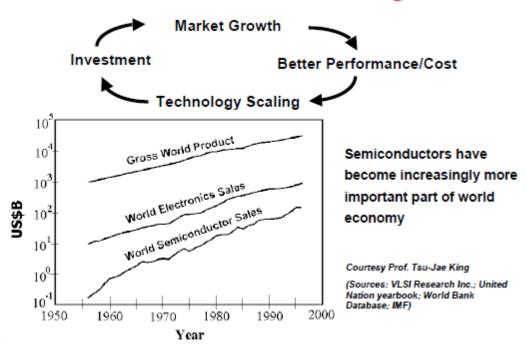

### Miniaturization => Market growth

### World IC Market by Technology

Silicon CMOS has become the pervasive technology

| Year                                 | 1997    | 1999    | 2003    | 2006    | 2009    | 2012    |

|--------------------------------------|---------|---------|---------|---------|---------|---------|

| Technology node (DRAM half pitch)    | 250 nm  | 180 nm  | 130 nm  | 100 nm  | 70 nm   | 50 nm   |

| Minimum Feature<br>Size              | 180 nm  | 120 nm  | 70 nm   | 60 nm   | 40      | 30      |

| DRAM Bits/Chip                       | 256M    | 1G      | 4G      | 16G     | 64G     | 256G    |

| DRAM Chip Size<br>(mm <sup>2</sup> ) | 280     | 400     | 560     | 790     | 1120    | 1580    |

| Microprocessor<br>Transistors/chip   | 11M     | 21M     | 76M     | 200M    | 520M    | 1.40B   |

| Maximum Wiring<br>Levels             | 6       | 6-7     | 7       | 7-8     | 8-9     | 9       |

| Minimum Mask<br>Count                | 22      | 22/24   | 24      | 24/26   | 26/28   | 28      |

| Minimum Supply<br>Voltage (volts)    | 1.8-2.5 | 1.5-1.8 | 1.2-1.5 | 0.9-1.2 | 0.6-0.9 | 0.5-0.6 |

Future projections for silicon technology taken from the SIA ITRS 1999

Ref. H. komiya IEEE ISSCC 1993

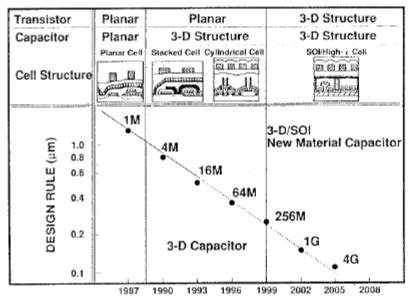

Device structures are becoming increasingly more complex

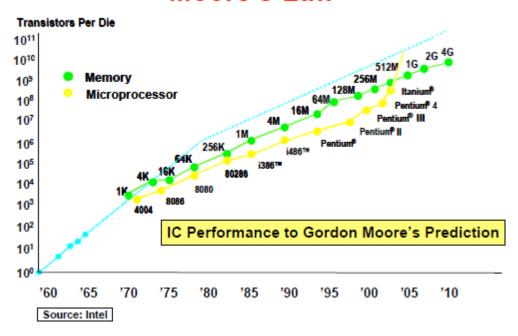

#### Moore's Law

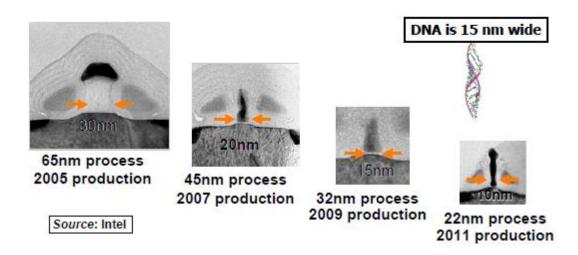

## Intel's Transistor Research down to 10nm

### Electronics is Nanotechnology

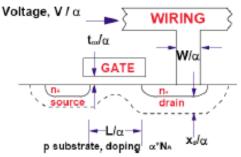

### MOS Device Scaling

#### Constant E Field Scaling

All device parameters are scaled by the same factor  $\alpha$ .

- Gate oxide thickness t<sub>ox</sub> ↓

- · Channel length L 1

- Source/drain junction depth X₁↓

- Channel doping †

- Supply voltage V<sub>D</sub> ↓

#### Why do we scale MOS transistors?

- Increase device packing density ~ α<sup>2</sup>

- 2. Improve frequency response (speed) ~ a

- Power/ckt: ~1/α², power density constant

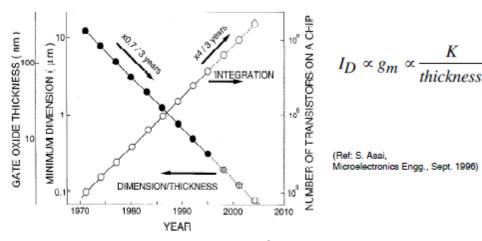

- Improve current drive (transconductance g<sub>m</sub>)

$$\begin{split} g_m &= \frac{\partial I_D}{\partial V_G} \bigg|_{V_D = const} \\ &= \frac{W}{L} \ \mu_n \ \frac{K_{ox}}{t_{ox}} \ V_D \qquad \qquad \text{for } V_D < V_{D_{SAT}}, \ linear \ region \\ &= \frac{W}{L} \ \mu_n \ \frac{K_{ox}}{t_{ox}} \left( V_G \ - \ V_T \right) \ \text{for } V_D > V_{D_{SAT}}, \ saturation \ region \end{split}$$

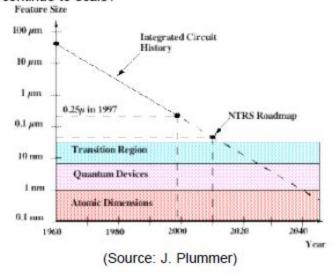

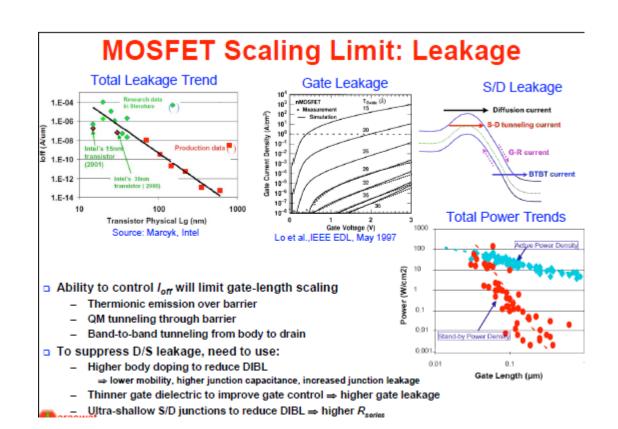

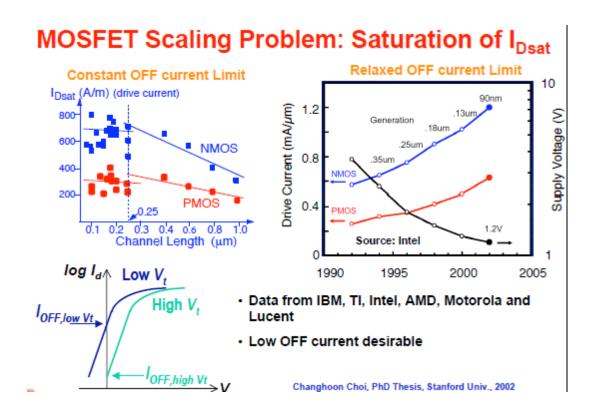

How far can we continue to scale?

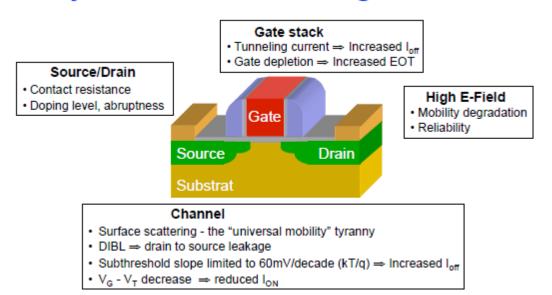

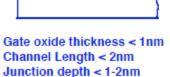

#### Physical Limits in Scaling Si MOSFET

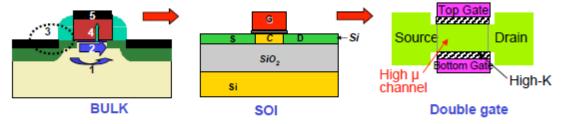

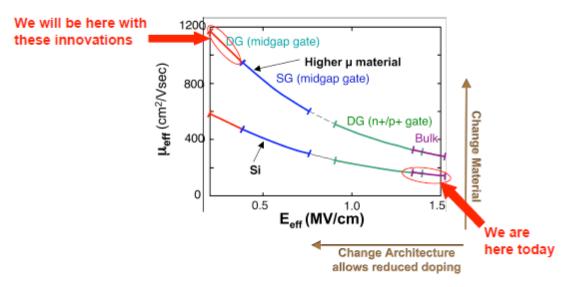

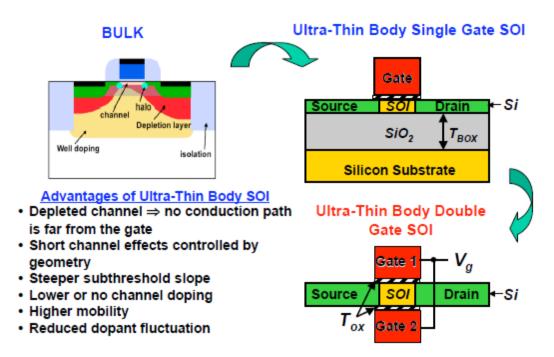

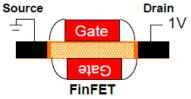

#### New Structures and Materials for Nanoscale MOSFETs

- 1. Electrostatics Double Gate

- Retain gate control over channel

- Minimize OFF-state drain-source leakage

- 2. Transport High Mobility Channel

- High mobility/injection velocity

- High drive current for low intrinsic delay

- 3. Parasitics Schottky S/D

- Reduced extrinsic resistance

- 4. Gate leakage High-K dielectrics

- Reduced power consumption

- 5. Gate depletion Metal gate

#### Combining New Device Structures with New Materials

- With better injection and transport we may be able to improve MOSFET  $I_{\rm ON}$

- With better electrostatics we may be able to minimize I<sub>off</sub>

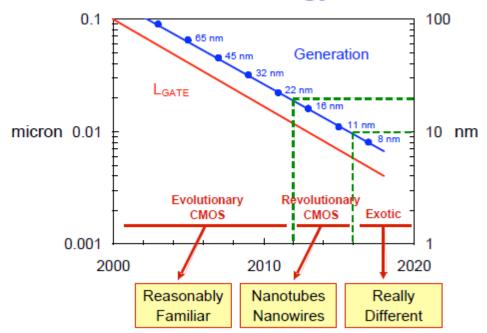

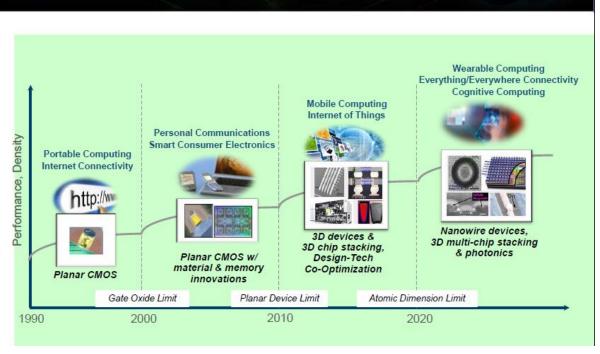

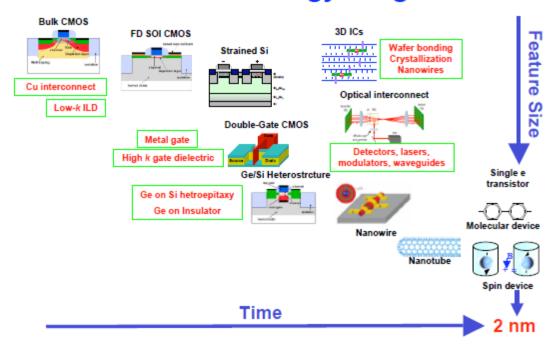

#### Nanotechnology Eras

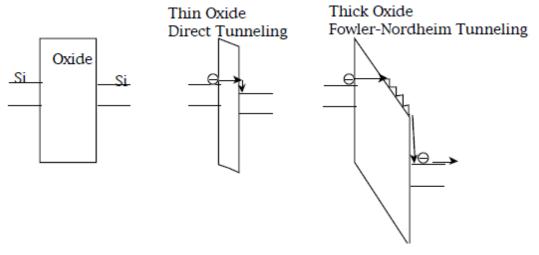

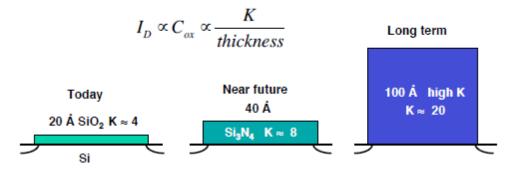

#### Scaling of MOS Gate Dielectric

Gate SiO<sub>2</sub> thickness is approaching < 10 Å to improve device performance

- · How far can we push MOS gate dielectric thickness?

- · How will we grow such a thin layer uniformly?

- · How long will such a thin dielectric live under electrical stress?

- · How can we improve the endurance of the dielectric?

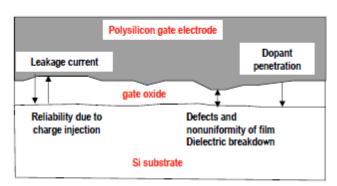

### Problems in Scaling of Gate Oxide

- Below 20 Å problems with SiO<sub>2</sub>

- Gate leakage => circuit instability, power dissipation

- Degradation and breakdown

- Dopant penetration through gate oxide

- Defects

#### Problems caused by conduction in ultrathin gate oxide

As we decrease the gate dielectric thickness, the conduction through the dielectric film becomes appreciable. This may increase power dissipation and cause problems for circuit stability. Increased leakage due to direct tunneling through the gate dielectric may make dynamic and static circuits unstable.

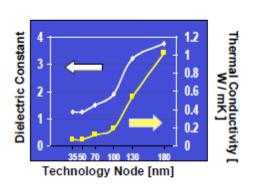

### High-k MOS Gate Dielectrics

$$I_{channel} \propto charge \ x \ source injection \ velocity  $\propto (gate \ oxide \ cap \ x \ gate \ overdrive) \ v_{inj}  $\propto C_{ox} (V_{GS} - V_T) \ E_{source} \ \mu_{inj}$$$$

Historically C<sub>ox</sub> has been increased by decreasing gate oxide thickness. It can also be increased by using a higher K dielectric

Higher thickness -> reduced gate leakage

#### Scaling of Ohmic Contacts and Junctions

- Device scaling dictates shallow junctions.

- . How will we form such shallow junctions?

- How will we make low resistance contacts to them?

- What will be the impact of the resistance of the contacts and junctions?

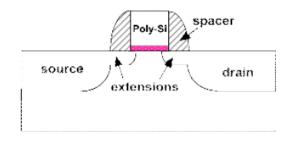

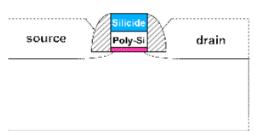

#### Solutions to Shallow Junction Problem

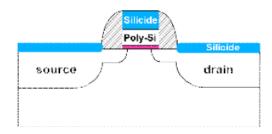

Shallow extension implants to minimize (DIBL)

Elevated source/ drain to minimize (DIBL)

Silicidation to junction minimize resistance

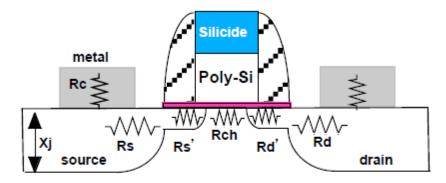

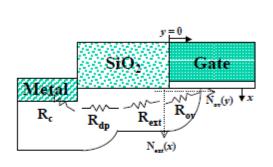

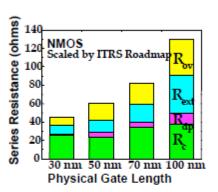

#### Source/Drain Resistance

Source: Jasonn Woo, UCLA

#### Problem in junction scaling:

- · Sheet resistance of a junction is a strong function of doping density

- · Maximum doping density is limited by solid solubility and it does not scale

- Silicidation can minimize the impact of junction sheet resistance (R<sub>s</sub>,R<sub>d</sub>)

- Contact resistance R<sub>c</sub> is one of the dominant components for future technology

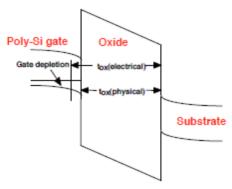

#### Problems with Poly-Si Gate.

This occurs because of high E - field due to a combination of higher supply voltage and thinner gate oxide.

- Effect of depletion is to increase effective t<sub>ox</sub> and thus reduce C<sub>ox</sub>

- A reduced C<sub>ox</sub> implies reduction in g<sub>m</sub> and thus I<sub>D</sub>(on)

- Ionized impurities in the gate electrode cause "remote charge scattering"

⇒ Reduced mobility

Need metal gate electrode with proper workfunction

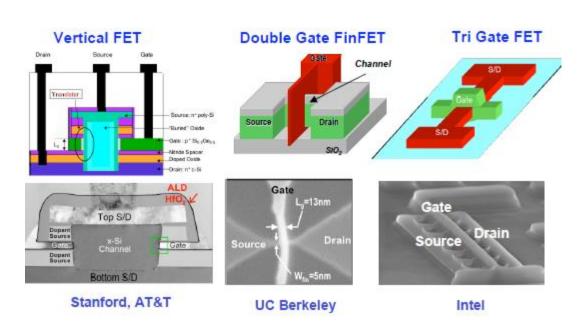

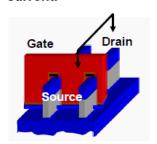

#### **Evolution of MOSFET Structures**

#### **Non Planar MOSFETs**

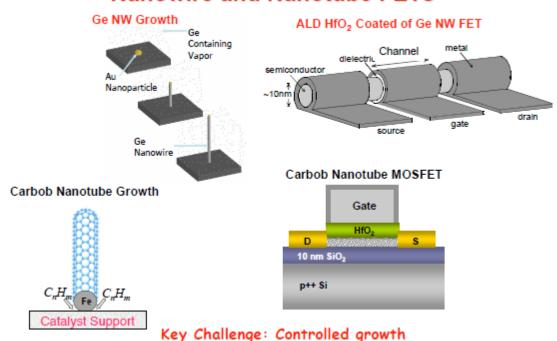

#### Nanowire and Nanotube FETs

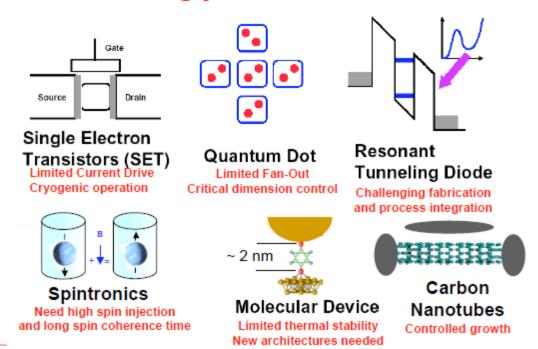

#### **Seemingly Useful Devices**

- In general this device scaling methodology does not take into account many other chip performance and reliability issues, e.g., interconnects, contacts, isolation, etc.

- These factors are now becoming an obstacle in the evolution of integrated circuits.

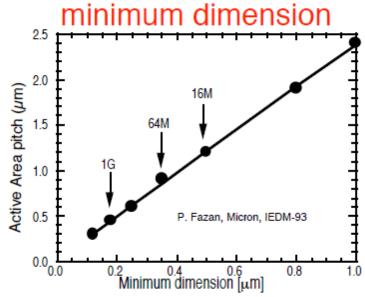

## Device Isolation pitch as a function of

With decreasing feature size the requirement on allowed isolation area becomes stringent.

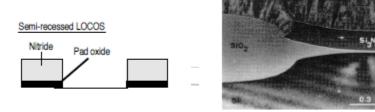

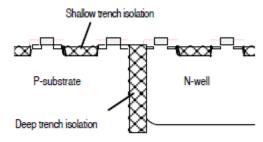

### Scaling of Device Isolation

LOCOS based isolation technologies have serious problems in loss of area due to bird's beak.

Trench Isolation can minimize area loss

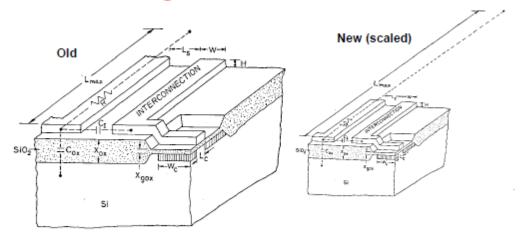

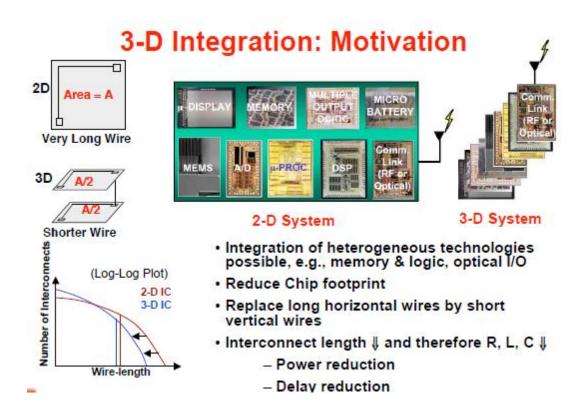

### Scaling of interconnections

- Bigger chip => longer interconnects

- Scaling to smaller dimensions => reduced cross section

- · Larger R, L and C

Higher Packing Density

↓

Decreased Space Between

Interconnects

↓

Higher RC-Delay

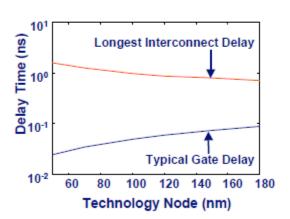

### Interconnect Delay Is Increasing

- Chip size is continually increasing due to increasing complexity

- Increase in R, L and C

- Device performance is improving but interconnect delay is increasing

- · Need better materials

- Metal with lower resistivity

- Dielectrics with lower K

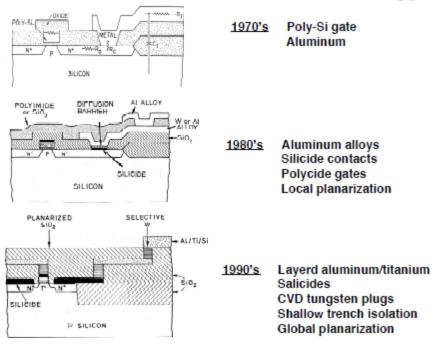

#### **Advances in Backend Technology**

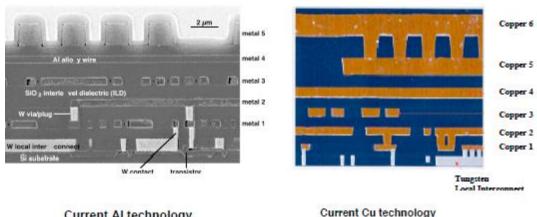

### Current Interconnect Technologies

Current Cu technology (Courtesy of IBM)

### Why Cu and Low-k Dielectrics?

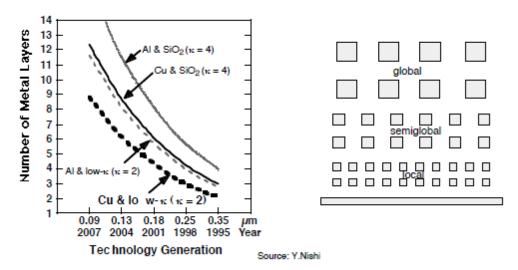

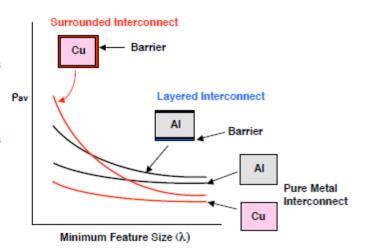

Reduced resistivity and dielectric constant results in reduction in number of metal layers as more wires can by placed in lower levels of metal layers.

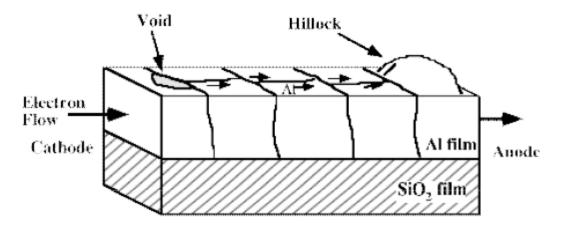

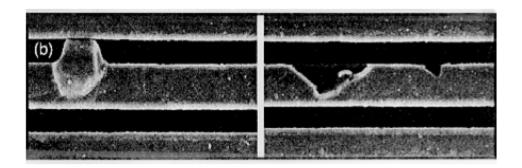

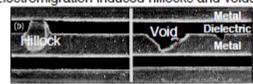

#### Electromigration

Electromigration due to electron wind induced diffusion of Al through grain boundaries

SEM of hillock and voids formation due to electromigration in an Al(Cu,Si) line

Mean time to failure due to electromigration is given by

$$MTF = \frac{A}{r^m J^n} \exp\left(\frac{E_a}{kT}\right)$$

### Problems in Scaling of Interconnections

#### AS λ DECREASES

- Resistivity increases as grain size decreases

- Resistivity increases as main conductor size decreases but not the surroundingbarrier size

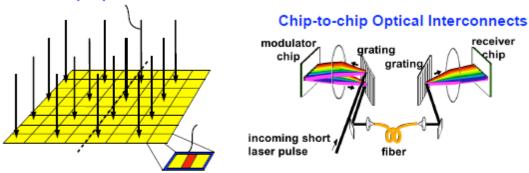

#### Can Optical Interconnects help?

**On-Chip Optical Interconnects**

Can potentially address many problems of Cu/low-k wires

- On-Chip Links

- ➤ Reduce delay

- Clocking and Synchronization

➤ Reduce jitter and skew

High Bandwidth off-chip Links

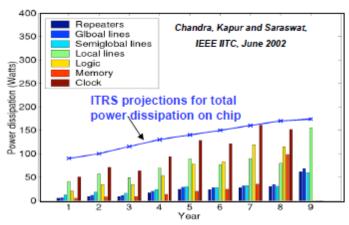

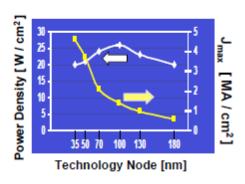

#### Result: scaling of power components

- Dynamic Power: CV<sup>2</sup>f

- Leakage power: devices

- · Short circuit power during switching

- Static power, e.g., analog components (sense amps etc.)

Power increasingly becoming the performance bottleneck for high-end microprocessors

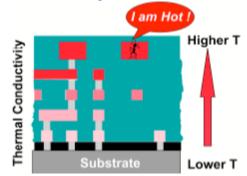

#### Thermal Behavior in ICs

- · Thermal conductivity of low-k insulators is poor

- Thermal impedance increases

- Energy dissipated (CV<sup>2</sup>f) is increasing as performance improves

- · Average chip temperature is rising

#### The problems Caused by Increased Power

>100A will flow on these wires

#### RELIABILITY

Electromigration induced hillocks and voids

Mean time to failure

$$MTF = \frac{A}{r^m J^n} \exp\left(\frac{E_a}{kT}\right)$$

10°C ↑, MTF ↓ 50%

#### **PERFORMANCE**

As T↑R↑, RC delay↑ 10°C↑, Speed↓5%

## Milestones in Our Industry 1964 Solid Logic Tech. ...... 2014 22nm CMOS Tech.

#### **IBM System 360**

The machine that defined the computer industry and the modern IBM

SLT module

#### 1964 - Transistor

6 transistors, 4 resistors

#### **IBM POWER8 Systems**

Open Innovation for Big Data, Cloud, and Analytics

#### 2014 - POWER8 Processor

22nm SOI eDRAM technology, 650mm<sup>2</sup> 12 cores and 96MB of on-chip memory 4.2 billion transistors

### Silicon Technology Scaling

### **Device Research Pipeline**

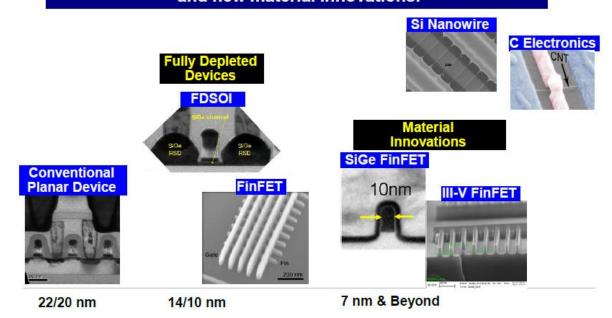

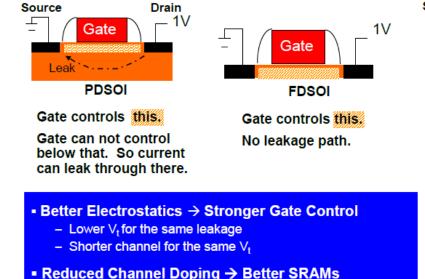

Scaling beyond 20nm requires alternative device structures and new material innovations.

### Device Innovation – Fully Depleted Devices

Less doping-driven threshold fluctuation

Lower supply voltage (V<sub>min</sub>) – by about 150mV

Lower voltages means lower power – up to 40%

Gates control this.

No leakage path.

Have more Si and thus can carry more current.

#### **Conclusion: Technology Progression**

### Summary

A Factory In 2010

Size of an atom ~ 5 Å

MOS Transistor in 2010

i reconstruction

A Circuit in 2010

Approaching \$10 billion 1010 components Integrated digital, analog, sensors

Questions we are trying to answer

- · How can we continue the Moore's law

- · What will be new materials, devices, circuits, sensors, equipment, simulators, etc.

- · How will we design them?

## Acknowledgements

- 1. Dr. Gary Patton, Vice President, IBM Semiconductor

- 2. Prof. Krishna Saraswat, Stanford University