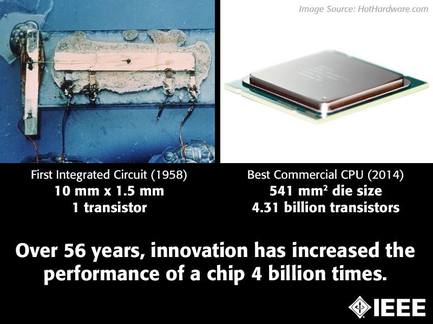

In 1958, Jack Kilby demonstrated the first integrated circuit (this is considered an IEEE milestone). Since then, microchip performance has followed the observations of Moore’s law. What that means is today’s chips are 4.3 billion times more powerful than Kilby’s first revolutionary circuit.

AVLSI Timing CLassification unit ppts

| avlsitiming_classification_of_digital_systems.pdf | |

| File Size: | 3397 kb |

| File Type: | |

BVLSI Experiements

| bvlsi_01.pdf | |

| File Size: | 243 kb |

| File Type: | |

| bvlsi_02.pdf | |

| File Size: | 263 kb |

| File Type: | |

| bvlsi_03.pdf | |

| File Size: | 40 kb |

| File Type: | |

| bvlsi_04.pdf | |

| File Size: | 132 kb |

| File Type: | |

| bvlsi_05.pdf | |

| File Size: | 46 kb |

| File Type: | |

| bvlsi_06.pdf | |

| File Size: | 146 kb |

| File Type: | |

| bvlsi_07_mux.pdf | |

| File Size: | 297 kb |

| File Type: | |

| bvlsi_08.pdf | |

| File Size: | 203 kb |

| File Type: | |

| bvlsi_09_full_adder_4.pdf | |

| File Size: | 406 kb |

| File Type: | |

| bvlsi_10.pdf | |

| File Size: | 414 kb |

| File Type: | |

AVLSI Experiment

| avls_expt_7.docx | |

| File Size: | 15 kb |

| File Type: | docx |

AVLSI PDFs

| avlsitiming_classification_of_digital_systems.pdf | |

| File Size: | 3373 kb |

| File Type: | |

| adv_vlsi_memory_rom.pdf | |

| File Size: | 1982 kb |

| File Type: | |

| avlsi_arithmetic_ckts.pdf | |

| File Size: | 3665 kb |

| File Type: | |

ANNOUNCEMENT

Please refer energy band diagram of MOS device under accumulation , inversion and depletion and MOSFET Capacitance topics strickly from CMOS Digital Integrated Circuits - Analysis and design by Sung Mo Kang

Please refer energy band diagram of MOS device under accumulation , inversion and depletion and MOSFET Capacitance topics strickly from CMOS Digital Integrated Circuits - Analysis and design by Sung Mo Kang

Energy band diagram of MOS device :Accumulation , inversion and depletion ( Latest)

| energy_band_diagram.pdf | |

| File Size: | 1092 kb |

| File Type: | |

Inverter Switching Characteristics ( Latest )

Note : this topic was not covered in class

Note : this topic was not covered in class

| inverter_switching_characteristics.pdf | |

| File Size: | 1301 kb |

| File Type: | |

POWER DISSIPATION IN CMOS CIRCUITS (LATEST)

Q . TYPES OF POWER DISSIPATION

Q. POWER DISSIPATION REDUCTION METHODS

Please Note : Read power dissipation pdf , before referring Sources of power dissipation

Q . TYPES OF POWER DISSIPATION

Q. POWER DISSIPATION REDUCTION METHODS

Please Note : Read power dissipation pdf , before referring Sources of power dissipation

| power__dissipation_in_cmos_circuits.pdf | |

| File Size: | 3650 kb |

| File Type: | |

SOURCES OF POWER DISSIPATION IN CMOS CIRCUITS ( LATEST)

| sources_of_power_dissipation_in_digital_cmos_circuits.pdf | |

| File Size: | 1668 kb |

| File Type: | |

Pass Transistor and Verilog ( Latest )

| pass_trans_verilog_vlsi_.pdf | |

| File Size: | 703 kb |

| File Type: | |

MOS CAPACITOR C-V Characteristics and Frequency effects ( Latest )

| mos_capacitor_cv.pdf | |

| File Size: | 2868 kb |

| File Type: | |

SHORT CHANNEL EFFECTS ( LATEST)

| short_channel_effects_in_mosfets.pdf | |

| File Size: | 567 kb |

| File Type: | |

Class ppts of VLSI Module 3 (Semiconductor Manufacturing Process)

| module_iii_vlsi.pdf | |

| File Size: | 2951 kb |

| File Type: | |

Syllabus for VLSI Mid Terms 2

1. Semiconductor manufacturing process Module ( Semiconductor manufacturing methods ( Mask Generation , Oxidation , CZ method , Photolithography , Ion implanatation , Diffusion and Metallization ) , Processing Steps for fabrication for Pmos , Nmos , Cmos p - Well , Cmos n-well , and Cmos twin tub process , CMOS LATCH -UP

2. Pass transistor and Transmission Gates ( 4:1 Mux , etc )

3. Mos inverter Module ( Concept of Noise Margin ( refer Univ Question and Kang ) , Resistive Load Nmos Inverter ( Derivation for Noise Margins + Numericals ) , Depletion load Mos Inverters ( Only Derivations ) , Inverter Sizing for one inverter driving another Inverter ( D-Load Nmos ) , CMOS Inverters ( Explanation and Derivation for 5 operation regions ) , Derivation for Switching or Threshold voltage for CMOS Inverters ( Plus Numericals) , Numericals on Noise Margins Calculation for a CMOS Inverter, VTC for CMOS Inverter inverter for different value of Kr.

1. Semiconductor manufacturing process Module ( Semiconductor manufacturing methods ( Mask Generation , Oxidation , CZ method , Photolithography , Ion implanatation , Diffusion and Metallization ) , Processing Steps for fabrication for Pmos , Nmos , Cmos p - Well , Cmos n-well , and Cmos twin tub process , CMOS LATCH -UP

2. Pass transistor and Transmission Gates ( 4:1 Mux , etc )

3. Mos inverter Module ( Concept of Noise Margin ( refer Univ Question and Kang ) , Resistive Load Nmos Inverter ( Derivation for Noise Margins + Numericals ) , Depletion load Mos Inverters ( Only Derivations ) , Inverter Sizing for one inverter driving another Inverter ( D-Load Nmos ) , CMOS Inverters ( Explanation and Derivation for 5 operation regions ) , Derivation for Switching or Threshold voltage for CMOS Inverters ( Plus Numericals) , Numericals on Noise Margins Calculation for a CMOS Inverter, VTC for CMOS Inverter inverter for different value of Kr.

Class ppts of VLSI Module 1

| vlsi_unit_1.pdf | |

| File Size: | 503 kb |

| File Type: | |

Class ppts of Design rules and Layout

| layouts_ds.pdf | |

| File Size: | 4395 kb |

| File Type: | |

Semiconductor Simulation Applets

http://jas.eng.buffalo.edu/

http://jas.eng.buffalo.edu/

BE Electronics Syllabus

| be_7-8-etrx___syllabus.pdf | |

| File Size: | 468 kb |

| File Type: | |

SEM 7 University Question Papers

| june_2014_etrx.pdf | |

| File Size: | 166 kb |

| File Type: | |

| december_2013_all_subjects_etrx.pdf | |

| File Size: | 363 kb |

| File Type: | |

| december_2012_all_subjects_etrx.pdf | |

| File Size: | 247 kb |

| File Type: | |

| june_2012all_subjects_etrx.pdf | |

| File Size: | 569 kb |

| File Type: | |

| may_2011all_subjects_etrx.pdf | |

| File Size: | 445 kb |

| File Type: | |

| december_2011all_subjects_etrx.pdf | |

| File Size: | 676 kb |

| File Type: | |

| december_2010all_subjectsetrx.pdf | |

| File Size: | 369 kb |

| File Type: | |

How a Intel Processor is made : Amazing process

| intel_chip_design.pdf | |

| File Size: | 322 kb |

| File Type: | |

| from_sand_to_circuits.pdf | |

| File Size: | 2355 kb |

| File Type: | |

Mosfet Transistor Basic

| 1.jpg | |

| File Size: | 1232 kb |

| File Type: | jpg |

| 2.jpg | |

| File Size: | 770 kb |

| File Type: | jpg |

| 3.jpg | |

| File Size: | 1311 kb |

| File Type: | jpg |

| 4.jpg | |

| File Size: | 937 kb |

| File Type: | jpg |

| 5.jpg | |

| File Size: | 959 kb |

| File Type: | jpg |

| 6.jpg | |

| File Size: | 1076 kb |

| File Type: | jpg |

CMOS INVERTER Slides

| 1.jpg | |

| File Size: | 1202 kb |

| File Type: | jpg |

| 2.jpg | |

| File Size: | 996 kb |

| File Type: | jpg |

| 3.jpg | |

| File Size: | 883 kb |

| File Type: | jpg |

| 4.jpg | |

| File Size: | 590 kb |

| File Type: | jpg |

| 5.jpg | |

| File Size: | 959 kb |

| File Type: | jpg |

| 6.jpg | |

| File Size: | 1076 kb |

| File Type: | jpg |

| 7.jpg | |

| File Size: | 759 kb |

| File Type: | jpg |

| 8.jpg | |

| File Size: | 1111 kb |

| File Type: | jpg |

| board_33_vlsi.jpg | |

| File Size: | 78 kb |

| File Type: | jpg |

| board_33_vlsi1.jpg | |

| File Size: | 87 kb |

| File Type: | jpg |

CMOS Digital Integrated Circuits - Analysis and design by Sung Mo Kang Topic wise Slides

| chapter1_vlsi_basic_.pdf | |

| File Size: | 2414 kb |

| File Type: | |

| physics_of_mos_transistor_.pdf | |

| File Size: | 4088 kb |

| File Type: | |

| chapter5_mos_inverter_.pdf | |

| File Size: | 2674 kb |

| File Type: | |

| chapter6_mos_inverter_dynamic_behaviour_.pdf | |

| File Size: | 5403 kb |

| File Type: | |

| chapter7_nand_and_nor_design_.pdf | |

| File Size: | 4240 kb |

| File Type: | |

Technical articles

| changing_the_transistor_channel.pdf | |

| File Size: | 170 kb |

| File Type: | |

| chipworks_reverse_engineering.pdf | |

| File Size: | 1853 kb |

| File Type: | |